emmtrix Code Vectorizer Now Supports RISC-V RVV – Powered by the Official RISC-V Vector C Intrinsics v1.0!

June 23, 2025

Introduction

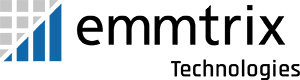

The RISC-V Vector Extension (RVV) has reached a key milestone: with the official ratification of the Vector C Intrinsics v1.0 in April 2025, scalable vector programming is now both portable and practical. To support this development, emmtrix Code Vectorizer now emits RVV code based on the standardized intrinsics — enabling automatic vectorization across a wide range of RISC-V hardware platforms.

Figure 1: From Sequential C Code to C Code with Vextor Extension for RISC-V

Why RVV Instrinsics – and Why Now?

The RVV specification has been under development since 2015, when UC Berkeley proposed a new approach to vector computing: scalable vector registers that avoid fixed-width constraints (such as 128 or 256 bits). Instead, RVV is length-agnostic, allowing the same code to run efficiently on a wide range of hardware — from embedded controllers to data center-grade vector cores.

In December 2021, the RVV v1.0 specification was officially ratified. It formalized essential features such as:

-

scalable vector registers

-

predicated operations

-

segment load/store instructions

These features are critical for achieving high throughput in modern computing environments.

Despite its potential, writing efficient RVV code has remained challenging. Unlike Arm SVE or x86 AVX, the dynamic behavior of RVV prevents the use of high-level operator overloading (+, *, etc.) through compiler vector extensions (GCC, Clang).

The RISC-V Vector C Intrinsics address this limitation. They provide a low-level but expressive C API, designed to closely map to hardware instructions, enabling the development of portable, maintainable, and readable vector code.

Following years of draft iterations (v0.9, v0.12), the specification reached maturity with the ratified version 1.0 in April 2025. This establishes a stable, toolchain-independent base for vector programming in the RISC-V ecosystem.

Compiler Support is Ready

Mainline compiler support is now aligned with the final spec:

-

GCC 14.1 supports draft version v0.12

-

Clang 17 supports v0.12 as well

-

Clang 20 introduces full support for v1.0

With compilers now supporting the standard, developers can transition from handwritten intrinsics and custom forks to a maintainable, standards-based workflow.

What emmtrix Code Vectorizer Brings to the Table

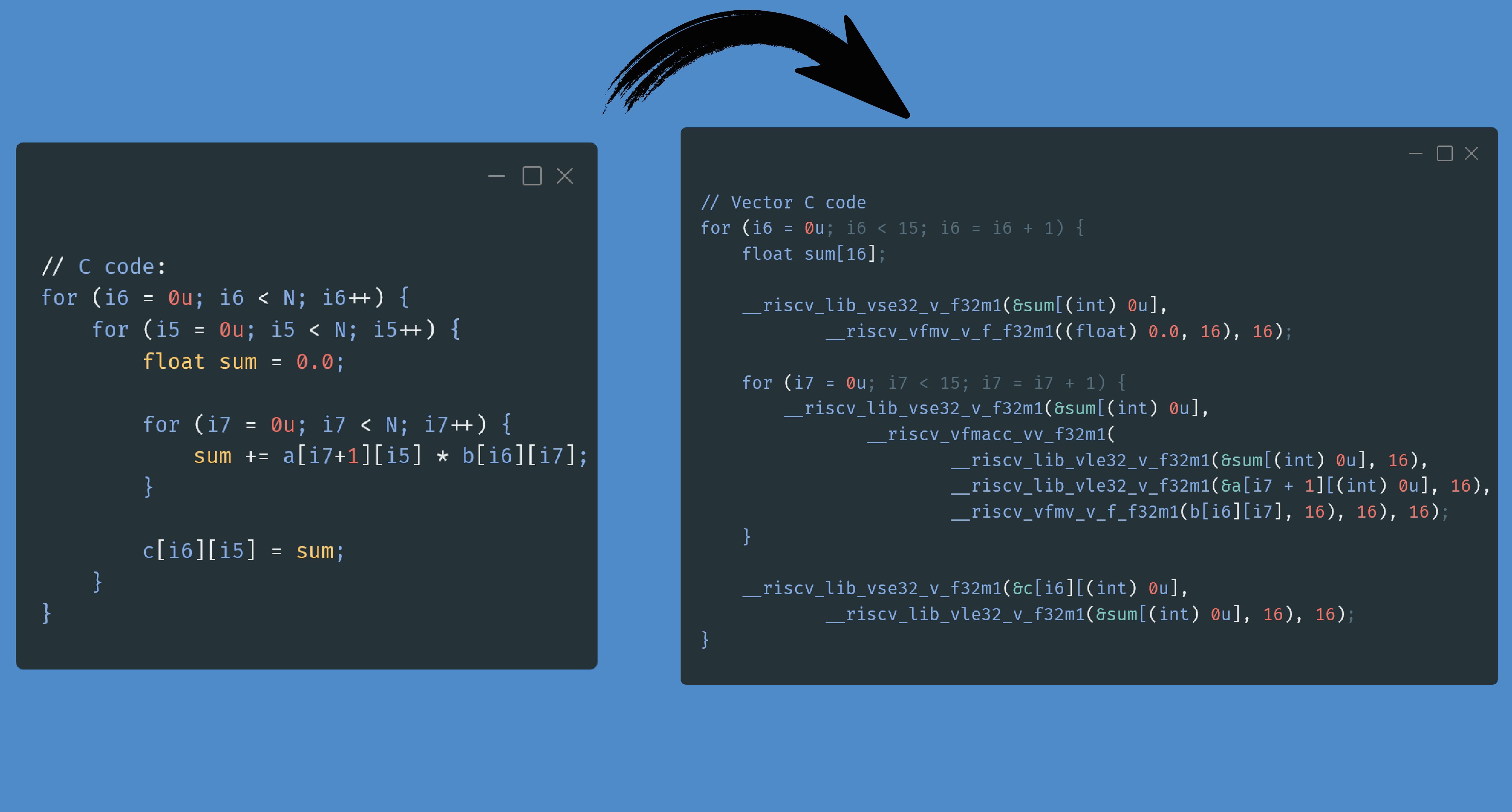

emmtrix Code Vectorizer has been updated to support automatic generation of RVV intrinsic code based on version 1.0. Starting from plain scalar C code, the tool emits optimized RVV code without the need to manually:

-

detect vector lengths

-

implement loop peeling

-

handle predicate masks

Key benefits:

-

Performance without manual tuning – abstraction and loop vectorization are handled by the tool

-

Readable, maintainable output – especially important for safety-critical domains

-

Toolchain compatibility – generated code compiles cleanly with upstream GCC and Clang

The result: high-performance vector code that runs efficiently across the RISC-V hardware spectrum — whether in automotive, embedded, or HPC domains.

Figure 2: C Code Vectorized for RISC-V Using emmtrix Code Vectorizer

Conclusion

With the RVV Vector C Intrinsics v1.0 now officially ratified and compiler support in place, the RISC-V ecosystem is ready for scalable, standards-based vectorization. emmtrix Code Vectorizer enables this transition by offering an automated, portable, and maintainable approach to RVV code generation.

📬 Contact us for a demo, evaluation, or technical discussion — we’re happy to hear about your use case.