emmtrix

Performance

Estimator (ePE)

Know Your Code’s Runtime – Without Running It

Static analysis for fast, detailed performance insights.

Why Static Estimation Makes a Difference

Performance estimation was never easier. With emmtrix Performance Estimator (ePE), developers can gain fast and accurate insights into the runtime behavior of their C code — without ever executing it. Unlike traditional simulation or hardware-based measurements, ePE applies static timing analysis early in the development process — and can be used at any later stage as well and typically delivers results up to six months ahead of a standard automotive HIL setup.

Automation & Reproducibility Built In

The analysis runs within minutes on the developer’s PC or can be integrated into a continuous integration (CI) system. The determined execution times are fully deterministic, offering consistent and reproducible results — a major advantage over measurement-based approaches, which can be influenced by non-deterministic runtime effects. This enables automated, project-accompanying performance tracking, allows for continuous monitoring of timing budgets, and makes it easy to evaluate runnables or SWCs even before full system integration.

Integrated into Model-Based Workflows

A standout feature of ePE is its seamless integration with code generated by TargetLink or Embedded Coder. Thanks to its static approach, ePE can assess even the smallest code fragments without measurement overhead. This enables precise timing insights down to the Simulink block level, empowering function developers with detailed understanding of their model’s performance — even in early development phases.

Key Benefits at a Glance

Early Static Timing Analysis

Design decisions before HIL

Simulink® and TargetLink® Support

Model-based code integration

No Code Exection Required

Static analysis directly on C code

CI/CD Integration for Deterministic Timing

Monitor timing changes during the development

Understanding Our Static Performance Estimation

Static performance estimation is a method for predicting the runtime behavior of software without executing it. This technique analyzes the program’s structure and instructions to estimate how long it will take to execute on a given processor.

Frequency x Cost: The Core Idea

Our method relies on a fundamental principle:

Execution Time = Execution Frequency x Execution Cost

The execution frequency is statically inferred from the control-flow structure of the code—for example, loops, conditional branches, and function calls. This allows us to approximate how often a block is executed during a typical run without requiring any runtime measurements.

The execution cost of each block is either:

- estimated by summing the costs of corresponding C statements (source level) or

- modeled via processor pipeline analysis (based on generated assembly).

Multi-perspective Timing Analysis

To provide a comprehensive view of a program’s timing behavior, our method estimates:

- Minimum

- Maximum

- Average execution times

By default, conditional constructs (e.g., if statements) are analyzed using a 50% branch probability, which can be overridden by the user to reflect domain-specific knowledge. This multi-perspective approach helps identify best- and worst-case scenarios and reveals runtime variability under different inputs.

Techniques to Refine Accuracy

Because static execution frequency determination is challenging, ePE uses several complementary techniques:

- Constant propagation across functions

Infers variable values across function boundaries to resolve control flows (e.g., loop bounds). - User-provided configuration data

Allows input of concrete values (e.g., from JSON, A2L, or DCM files) to refine estimations. - Manual specification

Enables developers to set loop bounds or probabilities when automation isn’t sufficient. - Analysis of ‘unknowns’

Performs sensitivity analysis to prioritize the most relevant manual inputs. - Use of host-level profiling data

Empirical values can override static assumptions when available.

Aggregating the Results

By applying the frequency-cost model to all code blocks, ePE aggregates total runtime. This allows:

- Identification of performance hotspots

- Early feedback of runnables and SWCs

- Support for automated performance tracking

Optional: Processor Pipeline Stages

The processor pipeline modeling considers stages such as:

Instruction Fetch

FETCH

Instruction Decode

DECODE

Shift + ALU

EXECUTE

Memory Access

MEMORY

Register Write

WRITE

Features

- Automatic generation of reports and visualization for more detailed information

- Confidence levels for classification of results

- Easy to integrate into the development workflow

- Fast evaluation for different target platforms

- Static performance estimation based on C code or assembly code

- Integration of simulators or hardware profiling into your workflow

What You Gain in Practice

- Performance estimation early in the development process

- Continuous monitoring of performance changes during the development

- Comparison of performance for different or heterogeneous target platforms

- Detailed information to better understand the timing behavior of your application

- Detect high-runners or critical parts of you software application

- Estimate the core utilization to optimize runnable/task to core mappings

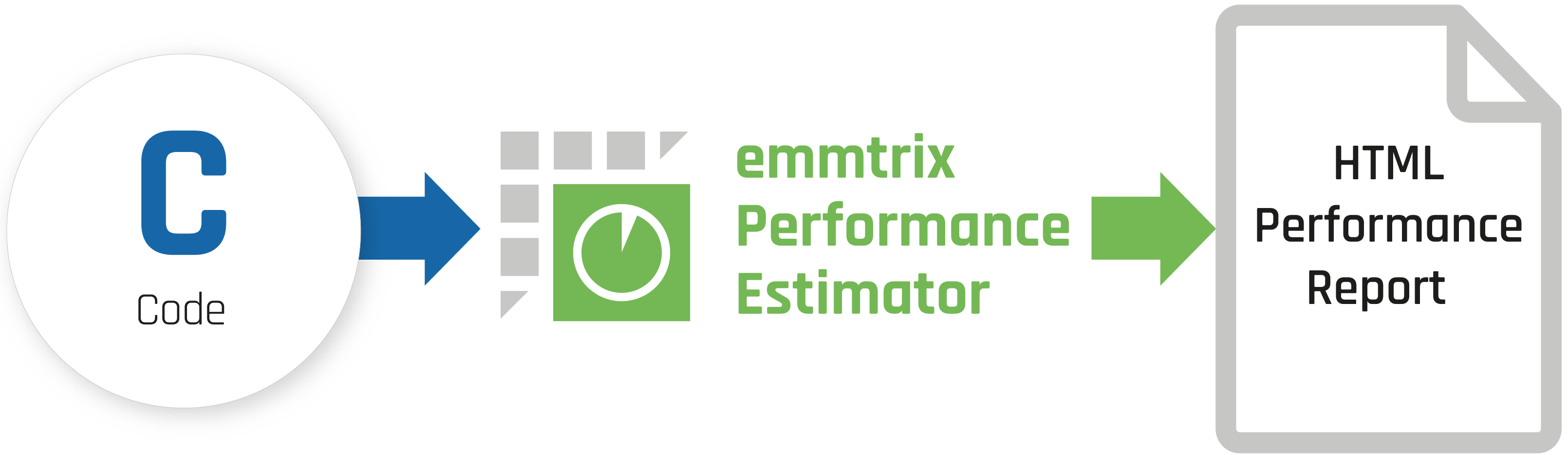

Intuitive Visualization

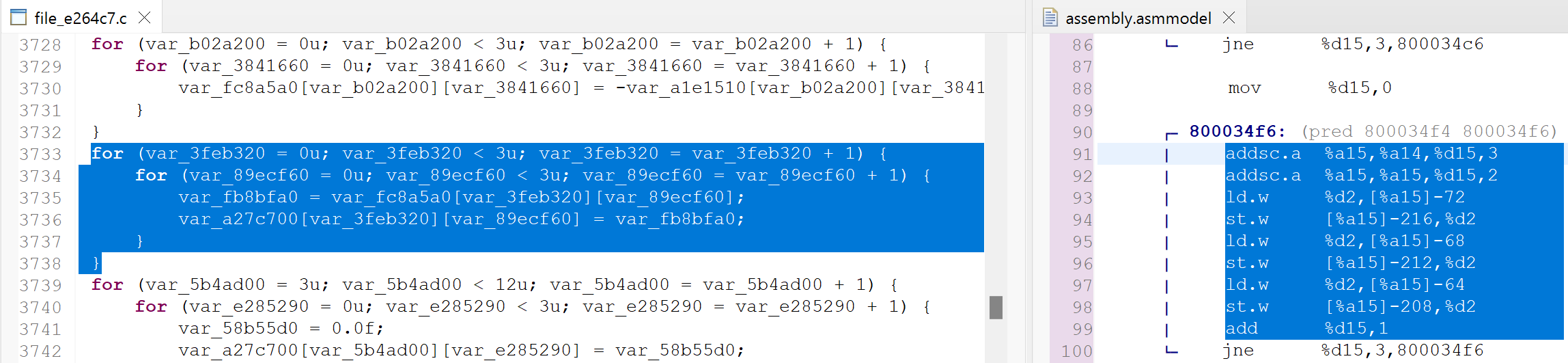

Figure 1: Visualization of the Performance Estimation

The result of the performance estimation can be visualized using our interactive and zoomable hierarchical program view. The X-axis represents the time, therefore the width of each block depends on the actual duration. On the Y-axis, the control structure of the program can be seen. Additional levels are added for structures like function calls, loops or conditions.

Figure 2: Analyzing Assembler Code

To enhance our static performance estimation solution, the emmtrix tools take applied compiler optimizations into consideration by analyzing assembler code. Together with a model of the processor pipeline, the actual timing behavior of the program on the selected hardware can be predicted with significantly higher accuracy. The advanced mapping between C and assembler code is accessed directly from the GUI and can be used for further inspection.

Some Supported Platforms

emmtrix Performance Estimator has already a wide range of supported target platforms ranging from general-purpose processors (e.g. ARM Cortex-A series or X86) to special-purpose microcontrollers (e.g. Infineon AURIX™ family). In general, the performance estimation can be easily adapted and customized to provide basic supoprt for new processor architectures. More complex and accurate hardware models with respect to the processor pipeline can be supported on demand.

Associated Partners

emmtrix Technologies is an Infineon Associated Partner with over 10 years of experience working with the Infineon AURIX™ microcontroller family and has been actively collaborating with Infineon for the past five years.

Extension & Integration for ePE

Simulink Performance

AUTOSAR Support

TargetLink Extension

CI/CD Workflow Integration

Let's Get in Touch

We believe that the best solutions start with a conversation. Whether you are exploring static code analysis, performance estimation, or code optimization – we’re here to help you reach your goals faster and more efficiently.